Puslaidininkinių komponentų gamyba apima daugybę sudėtingų gamybos procesų, skirtų žaliavoms paversti baigtais komponentais, skirtais įvairioms programoms, kurios atlieka svarbias valdymo ir jutimo funkcijas.

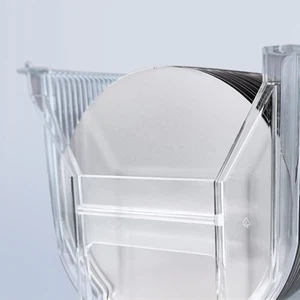

Puslaidininkių gamyba apima daugybę sudėtingų procesų, skirtų žaliavoms paversti galutiniais galutiniais komponentais. Puslaidininkių gamybos procesą paprastai sudaro keturi pagrindiniai etapai: plokštelių gamyba, plokštelių bandymo surinkimas arba pakavimas ir galutinis bandymas. Kiekvienas etapas turi savo unikalių iššūkių ir galimybių.

Puslaidininkių gamybos procesas taip pat susiduria su daugybe iššūkių, įskaitant sąnaudas, sudėtingumą, įvairovę ir našumą, tačiau taip pat suteikia puikių naujovių ir plėtros galimybių. Spręsdami sunkumus ir pasinaudodami galimybėmis, galime skatinti naujų technologijų kūrimą, kad pakeistume mūsų gyvenimo ir darbo būdą, kartu sudarant sąlygas pramonei toliau vystytis ir augti.

一. Puslaidininkių gamybos proceso apžvalga

Puslaidininkių gamybos procesą galima suskirstyti į šiuos pagrindinius etapus.

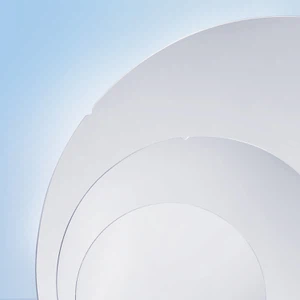

1. Vaflių ruošimas

Silicio plokštelės pasirenkamos kaip pradinė puslaidininkinio proceso medžiaga. Plokštelės valomos, poliruojamos ir paruošiamos naudoti kaip substratas elektroninių komponentų gamybai.

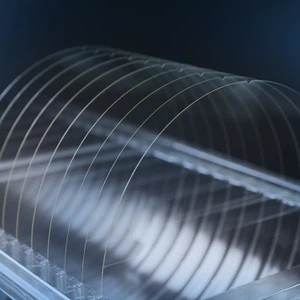

2. Raštai

Šio proceso metu modeliai sukuriami ant silicio plokštelių naudojant procesą, vadinamą fotolitografija. Ant plokštelės paviršiaus uždedamas korozijai atsparaus fotorezisto sluoksnis, o po to ant plokštelės uždedama kaukė. Kaukė turi raštą, atitinkantį atitinkamus iš anksto pagamintus elektroninius komponentus. Tada piešinys perkeliamas iš kaukės į fotorezisto sluoksnį naudojant ultravioletinę šviesą. Tada apšviestos fotorezisto sritys pašalinamos, paliekant raštuotą paviršių ant plokštelės.

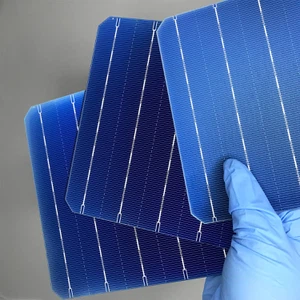

3. Medžiaginis dopingas

Šiame etape į silicio plokštelę pridedamos medžiagos, kad pakeistų jos elektrines savybes. Dažniausiai naudojamos medžiagos yra boras arba fosforas, kurių galima dėti nedideliais kiekiais, gaminant atitinkamai p arba n tipo puslaidininkius. Šios medžiagos yra implantuojamos į plokštelės paviršių naudojant jonų pagreitį, vadinamą jonų implantacija.

4. Vaflių nusodinimo apdorojimas

Šio proceso metu plonos plėvelės medžiagos nusodinamos ant plokštelės, kad būtų sukurti elektroniniai komponentai. Tai galima pasiekti naudojant įvairius metodus, įskaitant cheminį nusodinimą garais (CVD), fizinį nusodinimą garais (PVD) ir nusodinimą atominiu sluoksniu (ALD). Šie procesai gali būti naudojami medžiagų, tokių kaip metalai, oksidai ir nitridai, nusodinimui.

5. Ofortas

Dalies medžiagos pašalinimas nuo plokštelės paviršiaus, kad būtų sukurta elektroniniam komponentui reikalinga forma ir struktūra. ėsdinimas gali būti atliekamas naudojant įvairius metodus, įskaitant šlapiąjį ėsdinimą, sausąjį ėsdinimą ir plazminį ėsdinimą. Šiuose procesuose naudojamos cheminės medžiagos arba plazma, kad būtų galima pasirinktinai pašalinti tam tikras medžiagas iš plokštelės.

6. Pakuotė

Elektroniniai komponentai supakuojami į galutinį produktą, kuris gali būti naudojamas elektroniniuose įrenginiuose. Tai apima komponentų prijungimą prie pagrindo, pvz., spausdintinės plokštės, ir prijungimą prie kitų komponentų naudojant laidus ar kitas priemones. Puslaidininkių procesai yra labai sudėtingi ir apima įvairią specializuotą įrangą ir medžiagas. Šie procesai yra būtini gaminant šiuolaikinius elektroninius prietaisus ir toliau vystosi kartojantis naujas technologijas.

Paprastai puslaidininkinių lustų gamybos procesas trunka nuo kelių savaičių iki kelių mėnesių. Pradedant nuo pirmojo etapo, reikia pagaminti silicio plokštelę, kuri tarnautų kaip lusto pagrindas. Šis procesas paprastai apima šiuos procesus: valymą, nusodinimą, litografiją, ėsdinimą ir dopingą. Plokštelei gali tekti atlikti šimtus skirtingų proceso operacijų, todėl visas plokštelės gamybos procesas gali užtrukti iki 16-18 sav.

Kai atskiri lustai yra pagaminti ant plokštelės, juos reikia atskirti ir supakuoti į atskirus vienetus. Tai taip pat apima kiekvieno lusto patikrinimą, siekiant įsitikinti, kad jis atitinka specifikacijas, tada atskirti jį nuo plokštelės ir pritvirtinti ant pakuotės arba pagrindo. Kai lustai bus supakuoti, jie bus kruopščiai tikrinami, siekiant užtikrinti, kad jie atitiktų kokybės standartus ir pasiektų numatytas funkcijas. Tai apima elektroninių, funkcinių bandymų ir kitų tipų patikrinimo testų vykdymą, siekiant nustatyti defektus ar problemas. Tai taip pat priklauso nuo lusto sudėtingumo ir būtinų testavimo reikalavimų, todėl šis pakavimas ir testavimo procesas gali užtrukti 8-10 savaites.

Apskritai visas puslaidininkinių lustų gamybos procesas gali užtrukti kelias savaites ar mėnesius, nes tai priklauso nuo atitinkamų naudojamų technologijų ir lusto konstrukcijos sudėtingumo.

2. Puslaidininkių gamybos tendencijos ir iššūkiai

1. Rašto perkėlimas

Šablonų perdavimo technologijos pažanga tapo pagrindiniu sparčios puslaidininkių pramonės plėtros varikliu, leidžiančiu gaminti mažesnius ir sudėtingesnius elektroninius komponentus.

Didelė pažanga modelių perdavimo technologijoje yra pažangios litografijos, kuri yra šablonų perkėlimo į terpę, naudojant šviesos ar kitus spinduliuotės šaltinius, sukūrimas. Visų pirma, pastaraisiais metais sukurtos litografijos technologijos, tokios kaip ekstremalioji ultravioletinė (EUV) litografija ir kelių raštų technologija, naudojamos mažesnėms ir sudėtingesnėms grafikoms gaminti.

EUV litografija naudoja itin trumpo bangos ilgio šviesos pluoštus, kad sukurtų itin tikslius silicio plokštelių raštus. Ši technologija gali sukurti net kelių nanometrų dydžius, o tai būtina gaminant pažangius elektroninius komponentus, tokius kaip mikroprocesoriai.

Keli raštai yra dar viena litografijos technologija, kuri gali sukurti mažesnius raštus. Ši technologija apima vieno rašto suskaidymą į kelis mikropolinius modelius ir perkėlimą į plokštelės paviršių. Dėl to sukurtas raštas gali būti mažesnis už litografijoje naudojamą spinduliuotės bangos ilgį.

2. Dopingas

Priemonės – tai tam tikrų terpių pridėjimas prie silicio plokštelių, siekiant pakeisti jų elektrines savybes. Dopingo technologijos pažanga buvo pagrindinis spartaus puslaidininkių pramonės vystymosi veiksnys. Šią technologinę pažangą lėmė naujų dielektrinių medžiagų atsiradimas.

Tradiciškai boras ir fosforas yra dažniausiai naudojamos legiravimo medžiagos, nes iš jų galima pagaminti atitinkamai p ir n tipo puslaidininkius. Tačiau pastaraisiais metais buvo sukurtos naujos medžiagos, tokios kaip germanis, arsenas ir stibis, ir gali būti naudojamos sudėtingesniems elektroniniams komponentams gaminti.

Kitas dopingo technologijos pasiekimas yra tikslesnių dopingo procesų pažanga. Anksčiau jonų implantacija buvo pagrindinė dopingo technologija, apimanti didelės spartos jonų naudojimą dielektrikams implantuoti į plokštelės paviršių. Nors vis dar dažnai naudojamas jonų implantavimas, buvo sukurtos naujos technologijos, tokios kaip molekulinio pluošto epitaksija (MBE) ir cheminis nusodinimas garais (CVD), kad būtų galima tiksliau kontroliuoti dopingo procesą.

3. Nusodinimas

Nusodinimas yra dar vienas svarbus puslaidininkių gamybos procesas, kurio metu ant pagrindo nusodinama plona medžiagos plėvelė. Šis procesas gali būti pasiektas naudojant įvairias technologijas, tokias kaip fizinis nusodinimas garais (PVD), cheminis nusodinimas garais (CVD), nusodinimas atominiu sluoksniu (ALD) ir kt.

Tuo pačiu metu taip pat nuolat vystomos naujos technologijos, įskaitant metalų organinį cheminį nusodinimą garais (MOCVD), sustiprintą nusodinimą plazma, nusodinimą iš ritininio ritinio ir kt.

4. Ofortas

Odinimas apima tam tikrų puslaidininkinių medžiagų dalių pašalinimą, kad būtų sukurti raštai ar struktūros. ėsdinimo technologijos pažanga yra pagrindinė spartaus puslaidininkių pramonės vystymosi priežastis, taip pat pagrindinė technologija gaminant mažesnius ir sudėtingesnius elektroninius komponentus.

Anksčiau šlapiasis ėsdinimas buvo pagrindinė dažniausiai naudojama technologija, kuri apima plokštelės panardinimą į tirpalą, kuris ištirpina medžiagą. Tačiau šlapias ėsdinimas nėra tikslus ir gali pakenkti gretimoms konstrukcijoms.

Sausojo ėsdinimo technologijos atsiradimas leido tiksliau ir labiau kontroliuojamą ėsdinimo gamybą, pvz., reaktyvųjį jonų ėsdinimą (RIE) ir plazminį ėsdinimą. RIE yra technologija, kuri naudoja reaktyvius jonus selektyviai pašalinti medžiagą iš plokštelės, leidžiančią tiksliai valdyti ėsdinimo procesą.

Plazminis ėsdinimas yra panaši technologija, kuriai medžiagai pašalinti naudojama dujų plazma, tačiau ji turi papildomą naudą – selektyviai pašalina tam tikras medžiagas, tokias kaip metalai ar silicis.

5. Pakuotė

Pakavimo procesas puslaidininkių gamyboje apima integrinio grandyno inkapsuliavimą į apsauginį korpusą, kuris taip pat užtikrina elektros jungtis su išoriniu pasauliu. Pakavimo procesas turi įtakos galutinio produkto veikimui, patikimumui ir kainai.

3D pakavimas apima kelių lustų sudėjimą, kad būtų sukurtos didelio tankio integriniai grandynai. Ši technologija gali sumažinti bendrą įrenginio dydį ir pagerinti jo veikimą, kartu sumažinant energijos sąnaudas.

„Fan-out“ pakuotė – tai technologija, kurią naudojant integruotos grandinės įterpiamos į epoksidinio liejimo mišinio sluoksnį, naudojant iš lusto ištrauktus varinius stulpelius elektros jungtims. Ši technologija leidžia pakuoti didelio tankio pakuotę mažesnio dydžio.

„System-in-Package“ (SiP) yra dar viena technologija, sujungianti kelis lustus, jutiklius ir kitus komponentus į vieną paketą. Tai gali sumažinti bendrą įrenginio dydį ir pagerinti bendrą jo veikimą.